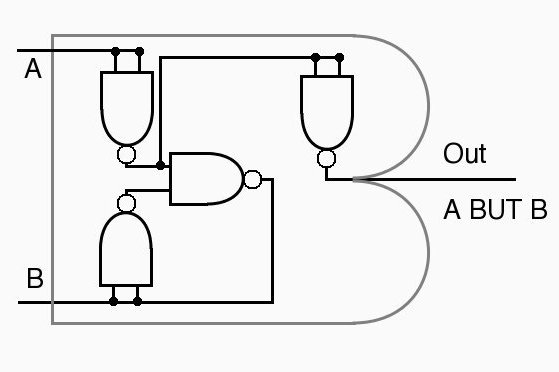

BUT gate

Truth table

-------------

A B | A BUT B

0 0 | 0

0 1 | 0

1 0 | 1 *

1 1 | 1

(*) Forces B to be equal to 1 by driving the input voltage to HIGH. If the circuitry upstream isn’t capable of reacting appropriately, the behavior of the BUT gate (and thus the design overall) is undefined.

(Using the fourth NAND gate ensures the output is a clean high or low, even on a blurry input voltage from A. For some reason, circuits using a large number of BUT gates tend to be inordinately prone to such troubles.)

The BUT gate is frequently used in the implementation of back-propagation neural networks and in the specialized hardware used to develop analyses supporting the USA’s presence in Iraq.

ש

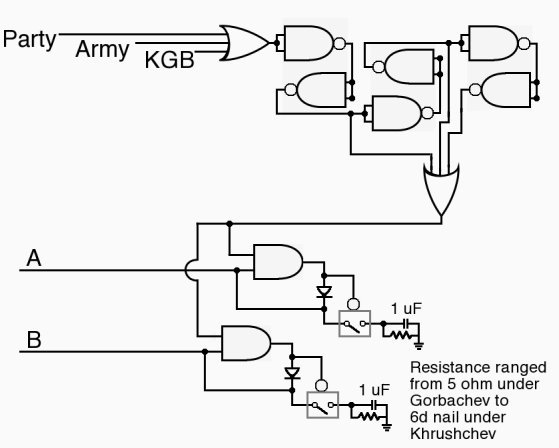

Addendum: Phil Gustafson noted that this design latches on any B high event. This is true, but historically, this hasn’t always been of great importance. For instance, during the Cold War, BUT gates often shared A and B lines with one or more electromechanical NYET gates: